-

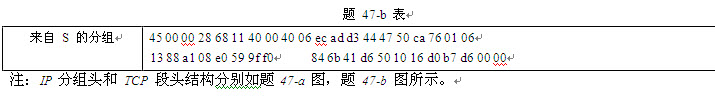

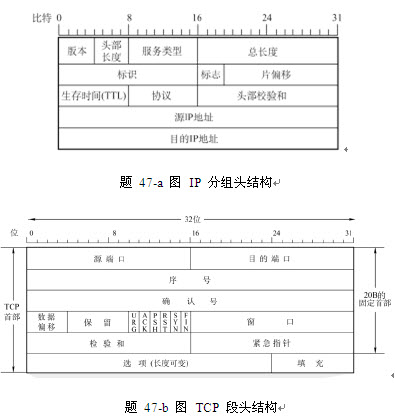

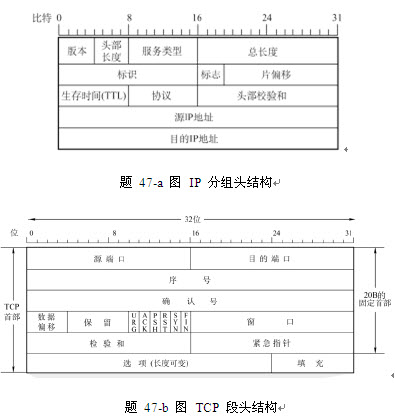

(9 分)主机 H 通过快速以太网连接 Internet,IP 地址为 192.168.0.8,服务器 S 的 IP 地址为 211.68.71.80。H 与 S 使用 TCP 通信时,在 H 上捕获的其中 5 个 IP 分组如 题 47-a 表所示。

回答下列问题。编号

IP 分组的前 40 字节内容(十六进制)

1

45 00 00 30 01 9b 40 00 80 06 1d e8 c0 a8 00 08 d3 44 47 50

0b d9 13 88 84 6b 41 c5 00 00 00 00 70 02 43 80 5d b0 00 00

2

43 00 00 30 00 00 40 00 31 06 6e 83 d3 44 47 50 c0 a8 00 08

13 88 0b d9 e0 59 9f ef 84 6b 41 c6 70 12 16 d0 37 e1 00 00

3

45 00 00 28 01 9c 40 00 80 06 1d ef c0 a8 00 08 d3 44 47 50

0b d9 13 88 84 6b 41 c6 e0 59 9f f0 50 f0 43 80 2b 32 00 00

4

45 00 00 38 01 9d 40 00 80 06 1d de c0 a8 00 08 d3 44 47 50

0b d9 13 88 84 6b 41 c6 e0 59 9f f0 50 18 43 80 e6 55 00 00

5

45 00 00 28 68 11 40 00 31 06 06 7a d3 44 47 50 c0 a8 00 08

13 88 0b d9 e0 59 9f f0 84 6b 41 d6 50 10 16 d0 57 d2 00 00

(1)题 47-a 表中的 IP 分组中,哪几个是由 H 发送的?哪几个完成了 TCP 连接建立过程?哪几个在通过快速

以太网传输时进行了填充?

(2)根据题 47-a 表中的 IP 分组,分析 S 已经收到的应用层数据字节数是多少?

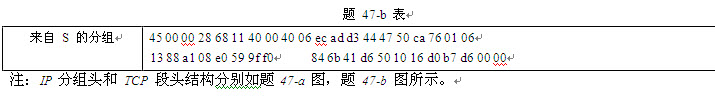

(3)若题 47-a 表中的某个 IP 分组在 S 发出时的前 40 字节如题 47-b 表所示,则该 IP 分组到达 H 时经过了多少个路由器?

-

(12 分)某 16 位计算机中,带符号整数用补码表示,数据 Cache 和指令 Cache 分离。题 44 表给出了指令系统 中部分指令格式,其中 Rs 和 Rd 表示寄存器,mem 表示存储单元地址,(x)表示寄存器 x 或存储单元 x 的内容。

题 44 表指令系统中部分指令格式

名称

指令的汇编格式

指令功能

加法指令

ADD Rs,Rd

(Rs)+(Rd)->Rd

算术/逻辑左移

SHL Rd

2*(Rd)->Rd

算术右移

SHR Rd

(Rd)/2->Rd

取数指令

LOAD Rd,mem

(mem)->Rd

存数指令

STORE Rs,mem

Rs->(mem)

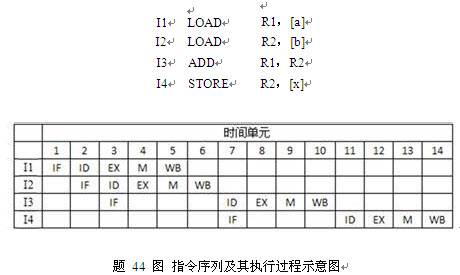

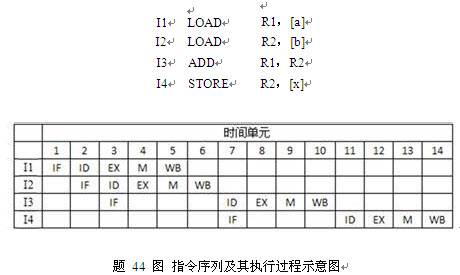

该计算机采用 5 段流水方式执行指令,各流水段分别是取指(IF)、译码/读寄存器(ID)、执行/计算有效地 址(EX)、访问存储器(M)和结果写回寄存器(WB),流水线采用“按序发射,按序完成”方式,没有采用转发

技术处理数据相关,并且同一寄存器的读和写操作不能在同一个时钟周期内进行。请回答下列问题。

(1)若 int 型变量 x 的值为-513,存放在寄存器 R1 中,则执行“SHL R1”后,R1 中的内容是多少?(用十六进制表 示)

(2)若在某个时间段中,有连续的 4 条指令进入流水线,在其执行过程中没有发生任何阻塞,则执行这 4 条指令 所需的时钟周期数为多少?

(3)若高级语言程序中某赋值语句为 x=a+b,x、a 和 b 均为 int 型变量,它们的存储单元地址分别表示为[x]、[a]和[b]。该语句对应的指令序列及其在指令流中的执行过程如题 44 图所示。

则这 4 条指令执行过程中 I3 的 ID 段和 I4 的 IF 段被阻塞的原因各是什么?

(4)若高级语言程序中某赋值语句为 x=x*2+a,x 和 a 均为 unsigned int 类型变量,它们的存储单元地址分别表示 为[x]、[a],则执行这条语句至少需要多少个时钟周期?要求模仿题 44 图画出这条语句对应的指令序列及其在流水 线中的执行过程示意图。

- A.SMTP、SMTP、SMTP

- B.POP3、SMTP、SMTP

- C.POP3、SMTP、POP3

- D.SMTP、SMTP、POP3

- A.仅 III、IV

- B.仅 I、II、III

- C.仅 I、II、IV

- D.I、II、III、IV

- A.180.80.76.0

- B.180.80.76.255

- C.180.80.77.255

- D.180.80.79.255

我

我